| Title            | Novel Quantum Wire Branch-Switches for Binary Decision Diagram Logic Architecture Utilizing Schottky Wrap-Gate Control of GaAs/AlGaAs Nanowires |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)        | Yumoto, Miki; Kasai, Seiya; Hasegawa, Hideki                                                                                                    |

| Citation         | Japanese Journal of Applied Physics. Pt. 1, Regular papers, short notes & review papers, 41(4B), 2671-2674 https://doi.org/10.1143/JJAP.41.2671 |

| Issue Date       | 2002-04                                                                                                                                         |

| Doc URL          | http://hdl.handle.net/2115/33082                                                                                                                |

| Rights           | Copyright © 2002 The Japan Society of Applied Physics                                                                                           |

| Туре             | article (author version)                                                                                                                        |

| File Information | kasai.pdf                                                                                                                                       |

Novel Quantum Wire Branch-Switches for Binary Decision Diagram Logic Architecture

Utilizing Schottky Wrap-Gate Control of GaAs/AlGaAs Nanowires

Miki Yumoto\*, Seiya Kasai and Hideki Hasegawa

Research Center for Integrated Quantum Electronics and Graduate School of Electronics and

Information Engineering, Hokkaido University, N13, W8, Kita-ku, Sapporo 060-8628, Japan

(received October 1, 2001; accepted for publication

A novel binary decision diagram (BDD) node device based on wrap-gate (WPG)

control of AlGaAs/GaAs nanowires is described and fabricated, and its basic operation is

characterized. The node device consists of one entry-nanowire branch and two exit-nanowire

branches where each of two exit-branches is switched by a Schottky WPG in a complimentary

fashion so as to realize path switching for electrons. Basic branch switches as well as BDD

node devices were fabricated on AlGaAs/GaAs nanowires formed by electron beam

lithography and wet chemical etching of molecular beam epitaxy (MBE)-grown

heterostructures. A detailed analysis of gate control characteristics was carried out by

magnetotransport measurements. A three-dimensional potential simulation showed that Fermi

level pinning on the semiconductor free surface should be carefully taken into consideration

for accurate device design. The branch-switch exhibited excellent gate control from low

temperatures up to room temperature, showing clear conductance quantization at low

temperatures. The fabricated BDD node device realized clear path switching from low

temperatures up to room temperature.

KEYWORDS: binary decision diagram (BDD), quantum wire (QWR), Schottky wrap gate

(WPG), path switching

\*Corresponding author. E-mail address: yumoto@rciqe.hokudai.ac.jp

1

### 1. Introduction

Needs for higher-density and higher performance integrated logic circuits are expected to continue to increase in future beyond the scaling-down limit of the Si complementary metal oxide semiconductor (CMOS) technology. Quantum large-scale integrated circuits (QLSIs) are promising candidates for next-generation nanoelectronics due to their inherently small switching delay-power products near the quantum limit. However, quantum devices are very weak and sensitive, and do not exhibit high device uniformity as demonstrated in Si devices. Therefore, quantum devices are not suitable for use in the conventional Boolean logic gate architecture used predominantly in the present-day Si CMOS LSIs with robust Si CMOS switching transistors. In order to realize QLSIs, it is necessary to adopt a novel logic architecture other than the Boolean logic gate architecture.

As a new alternative approach, we have recently proposed the use of the binary decision diagram (BDD) architecture<sup>1-3)</sup> which does not require robust switching. For hardware implementation of the BDD architecture, we have proposed to use our wrap-gate (WPG) technology<sup>4,5)</sup> to control quantum wires in order to realize an ultrasmall delay-power product near the quantum limit. For layouts of the BDD quantum circuits, we have proposed to use hexagonal nanowire networks for high-density integration.

The purpose of this paper is to investigate the feasibility of the new approach by fabricating and characterizing novel GaAs BDD node devices based on wrap-gate control of AlGaAs/GaAs nanowires formed by electron beam lithography and wet chemical etching of molecular beam epitaxy (MBE)-grown heterostructures.

# 2. Concept of Hexagonal BDD Quantum Circuits and Node Device Structure

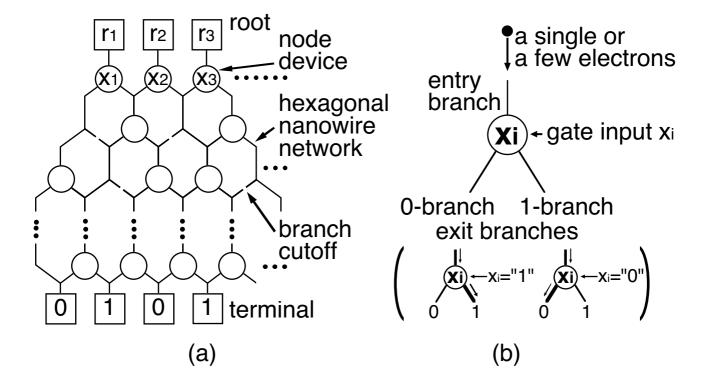

The binary decision diagram (BDD) scheme originally proposed by Akers<sup>6)</sup> is a representation scheme of a digital logic function by a directed graph. Its use in single electron circuits was first investigated by Asahi *et al.*<sup>7)</sup> using computer simulation. The hexagonal BDD quantum circuit approach proposed and partially fabricated by the authors' group<sup>1-3)</sup> consists of an array of quantum node devices formed on a hexagonal closely packed planar nanowire network, as schematically shown in Fig. 1(a). As shown in Fig. 1(b), each of the

BDD node devices consists of one-entry and two exit-branches, and its function is path switching, such that one of exit-branches is selected where the information messenger coming into the entry-branch goes out, depending on the gate input  $x_i$ . Here, the information messenger is either a single electron or a few electrons in quantum circuits, and path switching is realized by control of the quantum transport.

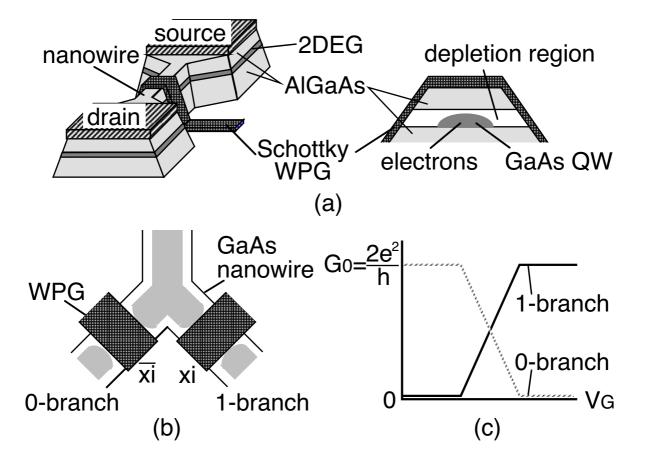

The novel GaAs BDD node device studied in this paper utilizes Schottky wrap-gate (WPG) control of quantum wires (QWRs). Figure 2(a) shows the basic structure of the WPG formed on a QWR<sup>4, 5)</sup>. A narrow Schottky gate is wrapped around an AlGaAs/GaAs nanowire having a trapezoidal cross-section. It realizes control of one-dimensional quantum transport by squeezing the nanowire by bias-controlled depletion. The WPG has a simple lateral structure suitable for fabrication and planar integration, and realizes tight gate control. The WPG BDD node device investigated in the present paper is schematically shown in Fig. 2(b). Here, a Y-shaped junction, consisting of one entry nanowire branch and two exit nanowire branches, is formed, and each of the exit-branches is controlled by a WPG branch-switch. By switching the two WPG branch-switches between the zero-th and first steps of conductance quantization in a complimentary fashion as shown in Fig. 2(c), the path switching function of the node device is realized. When the path switching is carried out through charging and discharging of sufficiently small gate capacitances with a few electrons, the switching delay-power product becomes near the quantum limit.

### 3. Fabrication and Characterization of Branch-Switches

The WPG QWR BDD branch-switches were fabricated in the following way. First, AlGaAs/GaAs heterostructure wafers having an n-GaAs cap were grown by MBE. The measured sheet carrier density and mobility at 1.8 K were  $5.6 \times 10^{11} \, \mathrm{cm^{-2}}$  and  $2.4 \times 10^5 \, \mathrm{cm^2/Vs}$ , respectively. The AlGaAs/GaAs nanowires were formed by electron beam (EB) lithography and wet chemical etching, using an  $H_2SO_4$ -based etchant. The Cr/Au Schottky WPGs were formed by EB lithography-based metal deposition and lift-off process after formation of source and drain Ge/Au/Ni ohmic contacts.

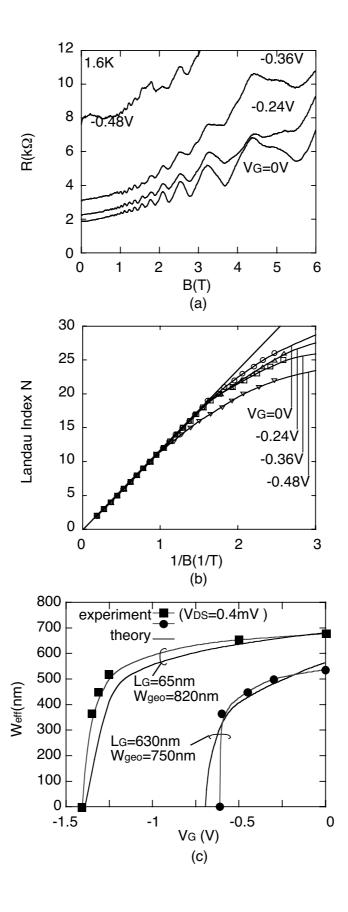

In order to clarify the control characteristics and the threshold voltage of the WPG

branch switch in detail, gate-dependent Shubnikov-de Haas (SdH) oscillation measurements were carried out. The results are shown in Fig. 3(a) for the branch devices shown in Fig. 2(a). Figure 3(b) shows the Landau plots for various gate voltages obtained from the SdH measurements. As seen in Fig. 3(b), one-dimensional constriction of electron cyclotron motion takes place in the WPG QWR branch-switch at various values of negative gate voltages. The values of the effective wire width,  $W_{\rm eff}$ , were estimated by fitting the experimental Landau plots to the theory based on the harmonic potential approximation  $(HPA)^4$ . The  $W_{eff}$  values obtained from the experimental Landau plots are compared in Fig. 3(c) for the two devices. One had a gate length,  $L_G$ , of 630 nm and a geometrical wire width,  $W_{\rm geo}$ , of 750 nm and, the other, with  $L_{\rm G}=65$  nm and  $W_{\rm geo}=820$  nm. As seen in Fig. 3(c), the WPG controls the potential in the nanowire efficiently and tightly near the pinch-off voltage of the wire. Thus, the quantum transport under the gated portion of the QWR is controlled tightly, resulting in low power switching with a very small voltage swing. It also allows high electrical conduction near zero gate bias. This means that the ungated portion of the QWR exhibits high conductance good for an interconnection. These characteristics are very favorable for use in our hexagonal BDD quantum circuits.

On the other hand, as seen in Fig. 3(c), the threshold voltage,  $V_{\rm th}$ , of a QWR piece with short- $L_{\rm G}=65$  nm was found to be much larger than that of the device with long- $L_{\rm G}=630$  nm, even though the devices were fabricated on the same epitaxial wafer. This shows presence of "a quantum device version" of the so-called short channel effect in the classical field effect transistors (FETs).

In order to understand this effect more quantitatively, a theoretical analysis was carried out, using a three-dimensional (3D) potential simulation program which solves the 3D Poisson's equation numerically. Since the present BDD node device requires nanometer dimensions, possible effects of the Fermi level pinning of the GaAs free surface were taken into consideration. The calculated theoretical  $W_{\text{eff}}$ - $V_{\text{G}}$  curves of the WPG structure are also shown in Fig. 3(c). It was found that experimental behavior could only be reproduced by assuming the presence of a strong Fermi level pinning at 0.8 eV from the conduction band minimum on the GaAs free surface<sup>8)</sup>. According to the calculation, the effect of Fermi level

pinning becomes larger and larger in the nanoscale devices, and it must be taken into consideration for QWR BDD node device design.

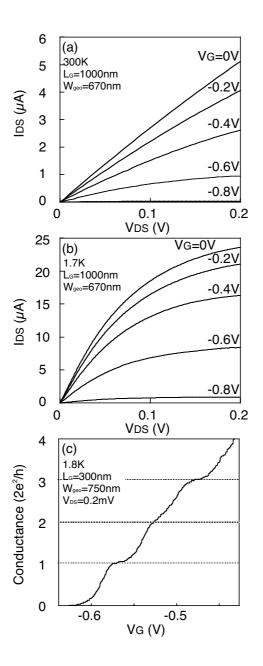

The fabricated WPG QWR branch-switches exhibited excellent gate control characteristics at low temperatures up to room temperature with complete channel pinch-off as shown in Figs. 4(a) and 4(b), respectively. Thus, the fabricated switches could be operated as normal FETs. The reason why the source-drain current,  $I_{DS}$ , increased at low temperatures is the increase of the electron mobility along the heterointerface. On the other hand, the wire pinch-off voltage was kept almost constant as expected, even when the temperature was changed. At low temperatures, the device having a suitable nanowire and WPG design<sup>8)</sup> showed tight gate control characteristics and a clear conductance quantization phenomenon at multiples of the quantized conductance unit,  $2e^2/h$ , as shown in Fig. 4(c).

# 4. BDD Path Switching Operation

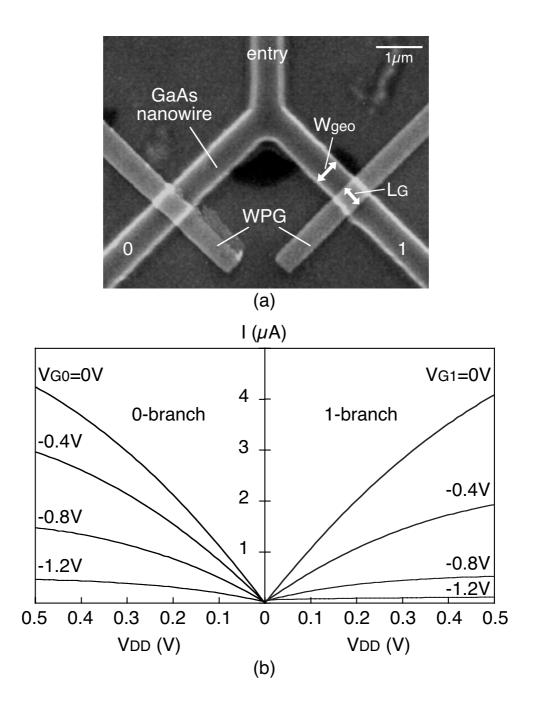

An SEM image of a fabricated WPG QWR-based BDD node device with two branch-switches is shown in Fig. 5(a). Path switching is realized by applying gate voltage pulse waveforms on WPG QWR branch-switches in a complimentary fashion. If each switch switches between the zero-th and first quantized steps of conductance, path switching near the quantum limit can be realized, as previously mentioned. The measured DC current-voltage characteristics on each exit-branch of the fabricated device at room temperature are shown in Fig. 5(b). In this device, each of the exit-branch had  $W_{\rm geo} = 300$  nm and  $L_{\rm G} = 1040$  nm. The node device showed good gate control characteristics like a conventional FET again, and current at  $V_{\rm G} = 0$  and  $V_{\rm th}$  on each branch were reasonably the same.

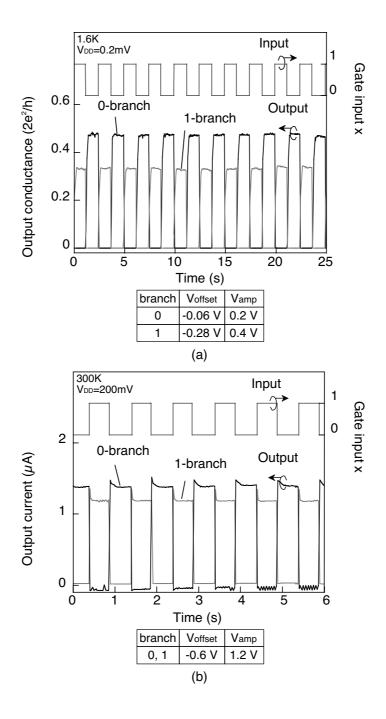

The path switching characteristics of the fabricated BDD node devices were measured under pulsed gate voltage conditions. The input and output waveforms used at 1.6 K are shown in Fig. 6(a). The bias conditions were adjusted as shown at the bottom of Fig. 6(a) in such a way that the device showed clear switching characteristics between the zero-th and first steps of quantized conductance on each branch. The heights of the quantized conductance steps were smaller than the ideal value of  $2e^2/h$  and this is most probably due to the reflection of electron waves that is known to be rather sensitive to the wire shape. The fabricated device

showed clear and correct path switching at low temperatures, as seen in Fig. 6(a). It showed correct path switching characteristics even at room temperature, as shown in Fig. 6(b). This is because the device operation changes gradually from a few-electron quantum regime to a many-electron classical regime with increase of temperature. At room temperature, the device operates correctly at an increased value of the delay-power product.

#### **5.** Conclusions

In this study, a novel AlGaAs/GaAs BDD node device based on wrap-gate control of nanowires was described, fabricated, and its basic characteristics were investigated. The conclusions are listed below:

- (1) The WPG realized a tight gate control of quantum transport near the wire pinch-off, and provided a high electrical conduction near zero bias. For design of gate control, Fermi level pinning on the semiconductor free surface should be carefully taken into consideration.

- (2) The branch switch controlled by a WPG exhibited excellent gate control of AlGaAs/GaAs nanowires from low temperatures up to room temperature, showing clear conductance quantization at low temperatures.

- (3) WPG BDD node devices were successfully fabricated on AlGaAs/GaAs nanowires, and they realized clear current path switching from low temperatures up to room temperature.

### Acknowledgements

The present work was supported financially in part by Grant-in-Aid for Science Research A (#13305020) and Science Research B (#12555083) from the Ministry of Education, Culture, Sports, Science and Technology.

### References

- 1) S. Kasai, Y. Amemiya and H. Hasegawa: *Tech. Dig. Int. Electron Devices Meet.* 2000 (2000) p. 585.

- 2) H. Hasegawa and S. Kasai: presented at *Advanced Workshop on Semiconductor Nanostructures*, Feb. 5-9, Queenstown, New Zealand, Physica E **10** (2001) 149.

- 3) S. Kasai and H. Hasegawa: Conf. Dig. 59th Device Res. Conf. (2001) p. 131.

- 4) S. Kasai, K. Jinushi, H. Tomozawa and H. Hasegawa: Jpn. J. Appl. Phys. 36 (1997) 1678.

- 5) S. Kasai and H. Hasegawa: Conf. Dig. 58th Device Res. Conf. (2000) p. 155.

- 6) S. B. Akers: IEEE Trans. Compt. C27 (1978) 509.

- 7) N. Asahi, M. Akazawa and Y. Amemiya: IEEE Trans. Electron Devices 42 (1995) 1999.

- 8) M. Yumoto, S. Kasai and H. Hasegawa: presented at *ICFSI-8*, June 10-15, Sapporo, Japan. To be published in Appl. Sur. Sci.

## Figure captions

- Fig. 1 (a) Concept of hexagonal BDD quantum circuit and (b) structure and function of BDD node device.

- Fig. 2 (a) Basic structure and cross-section of a WPG branch-switch on nanowire, (b) design of WPG BDD node device on AlGaAs/GaAs nanowire and (c) its operation.

- Fig. 3 (a) Gate bias dependent SdH oscillations, (b) their Landau plots of WPG branch-switch and (c)  $W_{\text{eff}}$ - $V_{\text{G}}$  curves from experimental and theory for WPG-controlled GaAs nanowires.

- Fig. 4 *I-V* characteristics of single WPG branch-switch at (a) 300 K and (b) 1.7 K, and (c) conductance characteristic at 1.8 K.

- Fig. 5 (a) SEM image of a WPG BDD node device and (b) DC *I-V* characteristics in exit-branches.

- Fig. 6 Path switching characteristics at (a) 1.6 K and (b) 300 K of WPG QWR-based BDD node devices.

Figure 1 M. Yumoto et al. (50%)

Figure 2 M. Yumoto et al. (50%)

Figure 3 M. Yumoto et al. (90%)

Figure 4 M. Yumoto et al. (80%)

Figure 5 M. Yumoto et al. (65%)

Figure 6 M. Yumoto et al. (80%)