| Title            | 「非晶質シリコン薄膜トランジスタのドレイン電流ドリフト特性とその機構」 |

|------------------|-------------------------------------|

| Author(s)        | 横山, 勇治; 大野, 英男; 長谷川, 英機; 下妻, 光夫     |

| Citation         | 北海道大學工學部研究報告, 140, 109-120          |

| Issue Date       | 1988-05-30                          |

| Doc URL          | http://hdl.handle.net/2115/42098    |

| Туре             | bulletin (article)                  |

| File Information | 140_109-120.pdf                     |

Instructions for use

# 「非晶質シリコン薄膜トランジスタのドレイン電流ドリフト 特性とその機構」

横山 勇治 大野 英男 長谷川英機 下妻 光夫

(昭和62年12月26日受理)

## Characterization and Mechanism of Drain Current Drift in Hydrogenated Amorphous Silicon Thin Film Transistor

Yuji YOKOYAMA, Hideo OHNO, Hideki HASEGAWA Mitsuo SHIMOZUMA (Recieved December 26, 1987)

#### Abstract

A theoretical and an experimental investigation of drain current drift in hydrogenated amorphous silicon thin film transistors (a-Si: H TFTs) is presented. Detailed measurements of drain current drift showed that the current drift characteristics are characterized by a very long time constant with time constant dispersion. A model involving interface states distributed energetically and spacially is presented which quantitatively explains the current drift phenomena.

#### 1. 緒 言

非晶質シリコン薄膜(以下、a-Si: H と記す)は、他の結晶半導体材料にない性質を備えているため、現在、太陽電池に代表される光電子素子及び薄膜トランジスタ(thin film transistor 以下 TFT と記す)に代表される電界効果素子と広範囲の分野への応用が期待されている。非晶質とは、原子配列に長距離秩序の存在しない状態をいう。一方、結晶とは原子が規則正しく配列し長距離秩序の存在する状態をいう。そのため、非晶質半導体の性質は、種々の要因を含み結晶半導体より複雑となる。非晶質半導体は、原子配列に長距離秩序を欠くものの完全に無秩序に原子が配列しているわけではなく、局部的に秩序を持つ短距離秩序が存在する。しかし一方では、結合の相手のない未結合手(dangling bond)も通常存在し、この未結合手は欠陥準位を形成する。a-Si: H において、この欠陥準位は、一般に局在準位(localized state)と呼ばれる。これまで、局在準位は、電界効果法<sup>11</sup>、容量-電圧法<sup>22</sup>、DLTS(deep level transient spectroscopy)法<sup>31</sup>、ICTS(isothermal capacitance transient spectroscopy)法<sup>41</sup>により評価され、グロー放電分解法により形成される a -Si: H 中の局在密度は  $10^{16}$ ~ $10^{19}$ ~cm<sup>-3</sup>・eV<sup>-1</sup>)であることが明らかとなっている。

a-Si: H は、現在種々のデバイスに用いられている単結晶シリコン(以下、c-Si と記す。)と比較すると種々の特徴・長所を有している。以下に記すと、(1)禁制帯幅は、c-Si において 1.1[eV]

電気工学科 電気物性工学講座

<sup>\*</sup> 電気工学科 医療技術短期大学部

であるのに対して a-Si: H では  $1.5\sim1.8$ (eV)と広い。(2)光吸収係数は,c-Si に比べ約 1 桁高い。(3)通常,a-Si: H は,シラン( $SiH_4$ )を原料ガスとしたグロー放電分解法によってガラス基板上に形成されるため,大面積化が容易である。(4)グロー放電分解法による a-Si: H 薄膜の形成において,n 層,p 層等のドーピング層の形成には,シランガスにホスフィン( $PH_3$ ),ジボラン( $B_2$   $H_6$ )ガスを混合するだけでよく,連続的に各層を形成できる。(5)チョクラルスキー法(CZ 法)による c-Si の形成温度は  $1400^{\circ}$ C 以上であるのに対して,グロー放電分解法による a-Si: H 薄膜の形成温度は  $250\sim300^{\circ}$ C である。そのため,a-Si: H は c-Si 形成時より製造電力が少ない。

これまで、a-Si: H 薄膜が注目を集めて来た最大の理由は、a-Si: H 特有の物理的性質よりも上述(5)の経済性の問題である。すなわち、a-Si: H 薄膜が他の半導体材料よりも安価に製造できることより、コストを大幅に減少させることができる。そのため、液晶ディスプレイの駆動素子として a-Si: H TFT<sup>5)</sup>、卓上計算機等の省電力用電源として a-Si: H 太陽電池<sup>6</sup>、ファクシミリ用として a-Si: H イメージセンサ<sup>n</sup>等が、すでに開発を終て民生用として市販されている。液晶ディスプレイは、現在、 $3\sim5$  インチと小型で主に OA (office automation) 機器用ディスプレイとして利用されている。しかし、今後、液晶ディスプレイが、より大型の CRT (cathode ray tube) ディスプレイと置き換わるためには、駆動素子の信頼性の向上及び高性能化が必要である。

a-Si: H 薄膜のデバイス応用において,問題点となるものの1つにデバイスの劣化現象がある。a-Si: H 太陽電池では,変換効率は時間とともに劣化することが報告されており,一方,a-Si: H TFT においては,ドレイン電流が時間とともに減少するドレイン電流のドリフト現象が観測されている。a-Si: H 太陽電池の劣化現象が,Steabler-Wronski 効果 $^8$  によるとされている $^9$  のに対して,a-Si: H TFT 劣化現象の詳細な機構は,明確ではない。

本報告は、以上の背景のもとで、a-Si: H TFT におけるドレイン電流ドリフト現象を解明するために、a-Si: H TFT を試作しドレイン電流のドリフト現象に関して、実験的及び理論的検討をおこなった。以下本報告では、本章に続き第二章で、試作したa-Si: H TFT の製作プロセスとその出力特性について述べる。第三章では、試作したa-Si: H TFT を用いてドレイン電流ドリフト特性を測定した。その結果、長時間にわたるドリフト現象の測定において、初期状態の設定が非常に重要であることが判明した。第四章では、初期状態を正しく設定したドリフト特性の測定結果が、界面準位が空間的に分布するモデル $^{10)11}$ (統一 DIGS モデル)により統一的に説明されることをドリフト特性のシミュレーションを用いて示した。統一 DIGS モデルは、H. Hasegawa et al が従来提案してきた「表面みだれモデル」 $^{12)13}$ を発展させたもので、絶縁一半導体、金属一半導体、半導体一半導体界面でのキャリヤのふるまいを矛盾なく説明することができるものである。第五章で本報告をまとめた。

## 2. 非晶質シリコン薄膜トランジスタの製作法と出力特性

## 2.1 非晶質シリコン薄膜トランジスタの製作プロセス

本節では、試作した非晶質シリコン薄膜トランジスタ (a-Si: H TFT)の製作プロセスについて述べる。コプレーナ型 a-Si: H TFT は、スタガー型に比べ寄生抵抗を小さくできる、また、高い伝達コンダクタンスを得ることが出来る等の理由から優れたスイッチング特性を期待することができる。コプレーナ型 a-Si: H TFT の製作において、一般に用いられる基板加熱を伴う絶縁膜形成法では、下地の a-Si: H 膜を劣化させてしまうため、低温(室温)プロセスが必要である。そこで、我々は、Shimozuma et al. が報告した低周波 (50 Hz) 室温プラズマ CVD シリコン窒化膜<sup>14)、</sup>をゲート絶縁膜として用いたコプレーナ型 a-Si: H TFT を製作した。

a-Si: H 膜は, 高周波 (13.56 MHz) 容量結合型グロー放電装置により成膜を行なった。成膜条 件を表-1に示す。放電ガスはシラン(SiH $_4$ )ガスを使用し、得られる undoped a-Si: H 膜の導電 率は  $10^{-10} \sim 10^{-8} [\text{S} \cdot \text{cm}^{-1}]$ である。シランガスにホスフィン $(\text{PH}_3)$ ガスを混入することにより n-type a-Si:H 膜を形成することができる。得られる n-type a-Si:H 膜の導電率は、 $10^{-2} \sim 10^{-1} [\text{S}\cdot\text{cm}^{-1}]$ である。

|   |   |   |   | _ |   |   |   |   |   |     |   |   |     | a-Si:H (i曆) Sii                                                       | N                                       |

|---|---|---|---|---|---|---|---|---|---|-----|---|---|-----|-----------------------------------------------------------------------|-----------------------------------------|

| F | r | e | q | u | e | n | с | у |   | Ĺ   | Н | z | ]   | 1 3 . 5 6 M H z 5 0                                                   |                                         |

| Т | e | m | р | е | r | а | t | u | r | e   |   | E | ( ع | 2 7 0 2 0                                                             | *************************************** |

| P | г | e | s | s | u | r | e |   | ι | Т   | 0 | r | r]  | 6.0 1.                                                                | 0                                       |

|   |   |   | Р | 0 | w | e | r |   | [ | w : | ] |   |     | 2 0 1 .                                                               | 0                                       |

| F | 3 | 0 | w |   | r | а | t | е |   | [   | s | С | см] | 50° 10<br>(10%H <sub>2</sub> 裕駅SiH <sub>4</sub> ) (SiH <sub>4</sub> ) |                                         |

表1 成膜条件とシリコン窒化膜の電気的特性

[\*n 層成額時: 50 (Si H<sub>4</sub>), 13 (1% H<sub>2</sub>希积 P H<sub>3</sub>)]

(SiN膜の 無気的特件)

屈折率 : 2.0

抵抗率 : 1 x 1 0 · <sup>5</sup> [Q · c m]

絶縁破壊電界強度 : 1~3 x 1 0° { V / c m }

比誘電率 : 6~8

プラズマ CVD (chemical vapor deposition)シリコン窒化膜は、現在、半導体集積回路に広く 利用されている。その主な理由は、(1)耐湿性が優れている(2)低温成長である(300°C程度)(3) 比誘電率が高い(4)段差被覆性が優れている、である。そのため、a-Si: HTFTのゲート絶縁膜 として多く用いられている。本報告では前述のように(1) Glass substrate ゲート絶縁膜として,低周波(50 Hz)室温プラズマCVD シリコン窒化膜を用いた。このシリコン窒化膜の成膜 条件及び電気的特性を表-1に示す。得られたシリコ ン窒化膜は、一般に用いられている基板加熱を伴う高 周波 (13.56 MHz) プラズマ CVD シリコン窒化膜の特性 と比較して遜色のないものである。

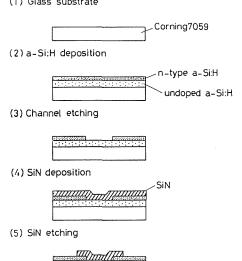

a-Si: HTFT製作プロセスの概要を図-1に示す。 まず、グロー放電装置により Corning 7059 ガラス基板 上に undoped a-Si:H 膜,n-type a-Si:H 膜を連続(4)SiN deposition 的に成膜する(図中(1)(2))。次に、チャネル部分の n-type a-Si: H 膜をエッチングし(図中(3)), 低周波 (50 Hz) 室温プラズマ CVD 装置によりシリコン窒化膜 (5) SiN etching を成膜する(図中(4))。最後に、ソース、ドレイン部 分のシリコン窒化膜をエッチングし(図中(5)),リフ トオフ法によりソース、ドレイン、ゲート A1 電極を形 (6) Evaporation 成する(図中(6))。n-type a-Si: H 膜は, ソース及び ドレイン部の A1 電極と undoped a-Si: H 膜との間に オーミック接触を取るために用いている。試作した a-

図1 a-Si: H TFT 製作プロセス

Si: H TFT の寸法は,チャネル長  $30(\mu m)$ ,チャネル幅  $1500(\mu m)$ ,シリコン窒化膜,undopeda-Si: H 膜,n-type a-Si: H 膜の膜厚は 1300(Å),6000(Å),500(Å) である。以下,測定は全で as-grown の試料に対して行ない,熱処理は行なっていない。

#### 2.2 試作トランジスタの直流出力特性

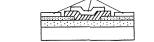

図ー 2 に試作した a-Si: H TFT の直流出力特性の結果を示す。横軸はドレイン電圧,縦軸はドレイン電流,ゲート電圧は 10(V)まで 1(V)ステップで掃引した。ドレイン電圧 10(V)で得られる最大のドレイン電流は  $7\times10^{-6}(A)$ となり,ON/OFF 電流比は約  $10^3\sim10^4$  である。a-Si: H 薄膜には,c-Si の場合と異なり局在準位が存在するため,その特性式は一般の MOS FET (metal-oxide -insulator field effect transistor) と異なるが,ここでは,通常用いる MOS FET 理論より,実効的な諸特性を導出・評価した。すなわち,飽和領域におけるドレイン電流の平方根とゲート電圧の関係より,その横軸との交点から閾値電圧を求め,傾きから実効移動度を求めた。

図ー2から得られたゲート電圧とドレイン電流の平方根との関係を図ー3に示す。局在準位が存在するにもかかわらず良い直線関係が得られている。これより関値電圧は1.15(V),飽和領域における実効移動度は $0.12(cm^2/V \cdot sec.)$ と求められた。また,伝達コンダクタンスには,最大 $3\times 10^{-6}$  [S/cm]である。これらの値は他の報告で述べられている一般的な値とほぼ同じ値である $^{15}$ )。

図 2 a-Si: H TFT 直流出力特性

3. 試作トランジスタの電流ドリフト特性

## 3.1 ドレイン電流ドリフトの測定法

本節では、a-Si: H TFT のドレイン電流ドリフト現象の測定法について述べる。Powell et  $al^{16}$ は、ゲート絶縁膜として用いるシリコン窒化膜中に電子捕獲準位が存在するため閾値電圧のシフト、ドレイン電流のドリフトが起こると報告している。金子他 $^{17}$ は、この閾値電圧のシフトに着目し閾値電圧シフトの温度、電圧、時間に対する依存性の実験式を導いた。一方、平中他 $^{18}$ は、シリコン窒化膜/a-Si: H 界面及び a-Si: H TFT 特性へのシリコン窒化膜の組成の影響を調べ、閾値電圧のシフトはシリコン窒化膜/a-Si: H 界面近傍に存在する欠陥準位によって生じると報告している。以上の報告例より、ドレイン電流のドリフト現象には界面近傍の半導体・絶縁体中の電子の捕獲準位が関与していると考えられる。

このような場合には、後にモデルのところで示すように捕獲・放出の時定数が極めて長くなる。 そのためドレイン電流のドリフトの測定結果は測定前の界面近傍の準位における電子の占有状態 に強く影響され、複雑なふるまいを示すものと予想される。そこで、我々は、ドレイン電流のド リフト現象を測定する際の初期条件に特に注意を払い、ドレイン電流のドリフト現象の起因を明 確にする測定を行なった。すなわち、ドレイン電流のドリフト測定のためのゲート電圧  $V_c$  を印加する前に、あらかじめ設定したゲート電圧  $V_o$  においてドレイン電流のドリフト特性を測定する。その後ドレイン電流が一定値に飽和するまで測定を続け、飽和したことを確認した後、ゲート電圧を  $V_c$  に設定してそのゲート電圧でのドリフト特性を測定する。このようにして初めて、初期状態の明らかな条件でドレイン電流ドリフトの測定が可能となるのである。

#### 3.2 ドリフト特性の測定結果

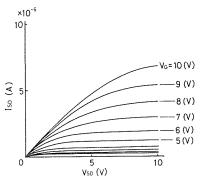

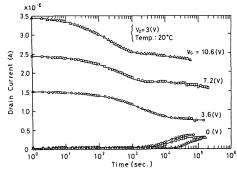

a-Si: H TFT のドレイン電流ドリフト特性の測定結果を図-4 に示す。ドレイン電圧 3(V), 測定温度  $20(\mathbb{C})$ 一定とし測定した。

図ー 4 中 No. 1 のデータは初期状態に特別の注意を払わなかったときのドレイン電流ドリフトの特性である。TFT を製作後すぐにゲート電圧 3.6(V) 印加し,ドレイン電流の時間変化を測定した。一方,No. 3 のデータはゲート電圧を 0(V) に保ちドレイン電流が飽和したことを確認した後(図ー4 中 No. 2),ゲート電圧を  $0(V) \rightarrow 3.6(V)$  としてドレイン電流の時間変化を測定したものである。図ー 4 から明らかなように,No. 1 は増加及び減少形の入り交じった複雑なドリフト特性を示し

図一4から明らかなように、NO.1は増加及び減少形の入り交じった複雑なドリフト付任を示しているのに対し、No.3は減少形ドリフトしか見られていない。このように、ゲート電圧 0[V]において、十分長時間 TFT を保持することにより界面近傍の準位の電子分布が定常状態に達した後測定した No.3の場合と、初期状態に特別な注意を払わなかった No.1の場合とでは、ドリフトのふるまいが大きく異なっている。また、No.2において、電流が飽和するのに 20 時間程度かかっている。このことから、ドリフト現象の測定において解析に耐えうるデータを得るためには、ドリフト現象がきわめて長時間にわたることを考慮にいれた初期状態の設定が非常に重要であることがわかる。

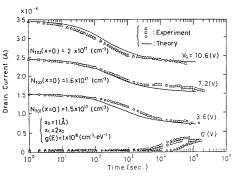

次に、各ゲート電圧におけるドレイン電流ドリフト特性の測定結果を図-5に示す。ドレイン電圧 3(V)、測定温度  $20(^{\circ}C)$ 一定とし、印加ゲート電圧は 3.6、7.2、10.6(V)である。長時間にわたるドリフト特性の測定において初期状態の設定が電流ドリフトのふるまいに大きな影響を及ぼすことから、各ゲート電圧でのドリフト測定前にゲート電圧 0(V) においてドレイン電流が一定値に飽和したことを確認した後測定を行なった。図-5 より、各ゲート電圧におけるドリフト特性は、ほぼ同じ傾向を示していることがわかる。また、ゲート電圧の増加とともにドリフト特性は、短時間側へシフトしている。

図4 ドレイン電流ドリフトの測定結果

図5 各ゲート電圧におけるドレイン電流ド リフトの測定結果

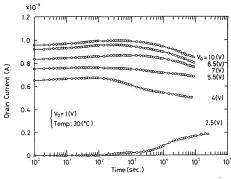

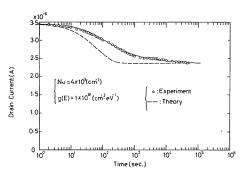

次に、ゲート電圧の印加手順を変えて行なった、各ゲート電圧におけるドレイン電流ドリフト特性の測定結果を図ー 6 に示す。ドレイン電圧 1(V)、測定温度  $30(^{\circ}C)$ 一定とした。測定は、次の手順に従い行なった。まず、ゲート電圧 2.5(V)においてドレイン電流が一定値に飽和したことを

図 6 各ゲート電圧におけるドレイン電流ド リフトの測定結果

確認した後,ゲート電圧を 2.5 V から 4(V)にステップ状に変化させドレイン電流の時間変化を測定した。約  $10^5$  秒後,ゲート電圧を 4(V) から 5.5(V) に変化させ,その後のドレイン電流の時間変化を測定した。以下,同様に約  $10^5$  秒後にゲート電圧を変化させた。図ー 6 において,電流ドリフトのふるまいは図ー 5 と異なる。また,ゲート電圧の増加とともに電流ドリフトの短時間側へのシフトは見られず逆に長時間側へシフトしている。

#### 4. 電流ドリフトに関する新しいモデル

#### 4.1 MIS C-V 特性と界面準位

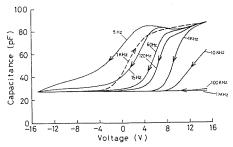

本節では、a-Si: H MIS(Metal-Insulator-Semiconductor) ダイオードによる C-V 特性の測定 結果, 及びその界面準位との関係について述べる。

a-Si: H MIS ダイオードは,以下の手順で製作した。 $n^+c-Si(\langle 100\rangle)$ ,抵抗率  $0.002\sim 0.005(\Omega \cdot cm)$ )上にグロー放電分解装置により a-Si: H undoped 層  $(6000\,\text{Å})$ ,n-type 層  $(500\,\text{Å})$  を連続的に成膜する。次に n-type 層をエッチングし,その後,低周波  $(50\,\text{Hz})$  室温プラズマ CVD 装置によりシリコン窒化膜  $(1300\,\text{Å})$  を形成した。シリコン窒化膜の形成は,a-Si: H TFT と同時に行なった。

図 7 a-Si: H MIS ダイオードによる C-V 測定結果

図一7にC-V特性の測定結果を示す。直流バイアス掃引範囲を $+15\sim-15(V)$ とし,直流バイアス掃引速度を45(mV/sec.)とした。また,測定周波数  $1\,k\text{Hz}$  におけるヒステリシス現象の結果も合わせて示す。各周波数におけるC-V 特性のふるまいは,これまで原他が報告した結果 $^{19}$  と同じふるまいを示している。低周波数において,C-V 曲線は $_{-1}$  所で特徴的なふるまいを示している。原他によると,0(V)付近での容量の急激な減少は,キャリヤの充放出時定数が測定周波数に追従できなくなるためであり,

10(V)付近での容量の変化は界面準位密度の分布形状を反映したものである。また、周波数の増加とともに C-V 曲線は、順バイアス側にシフトしている。これは、周波数が高くなるにつれ、伝導帯付近の準位しか測定周波数に追従できなくなるからである。

原他<sup>20</sup> は, a-Si: H MIS C-V 特性においてコンピュータシミュレーションによる詳細な解析の結果, 周波数依存性での複雑なふるまいはバルク局在準位では説明することができず, 界面準位を考慮した系でのみ再現できることを示した。さらに, 有本他<sup>21)</sup> は, ICTS 法による検討の結果, a-Si: H MIS 構造の電気的特性を支配しているのは, 従来考えられていたバルク局在準位でなく絶縁体/半導体界面付近に存在する界面準位であることを示唆した。a-Si: H MIS C-V 測定結果及び上述の報告例から, a-Si: H TFT におけるドレイン電流のドリフト現象とバルク局在準位ではなく界面準位に起因すると考えられる。

また,界面準位を考えるに当たって,界面準位が絶縁体/半導体界面に局在すると考えると,後

で示すようにドレイン電流のドリフト現象で測定される時定数分散及び長い時定数を説明することが困難となる。一方,化合物半導体 MIS 界面における界面準位の発生機構及びその電気的特性は,Hasegawa and Ohno が最近報告した統一 DIGS (disorder induced gap state) モデルによって統一的に説明されることが示されており  $^{11}$ , このモデルに基づいて化合物半導体 MIS FET におけるドレイン電流のドリフト現象が,チャネル内の電子が界面近傍に空間的に分布する DIGS すなわち界面準位に捕獲放出されることにより引き起こされることが明らかにされている $^{10}$ 。さらに a-Si: H TFT のドレイン電流ドリフトのふるまいと化合物半導体 MIS FET のそれとは,ともに長い時定数と単一の時定数で記述できない時定数分散を有することから,a-Si: H TFT のドレイン電流ドリフトについても,界面準位が空間的に分布していると考えるのが妥当と思われる。

このことより,以下の 4.2 節では a-Si: H MIS 界面において界面準位が空間的に分布している場合のドレイン電流ドリフトのふるまいを定式化し,4.3 節において実験結果と計算結果を比較した。

#### 4.2 空間分布した界面準位に基づく電流ドリフトのモデル

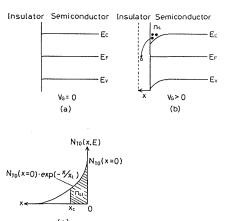

n チャネルの TFT を考える。TFT のゲートに正の電 Insulator Semiconductor Insulator Insulator Semiconductor Insulator Insulator Semiconductor Insulator Insul

以下では,この考えを前提に,まず,(1)電流ドリフトの計算において基本となるドレイン電流と捕獲される電子密度との関係を示し,その後,(2)局在準位の存在を考慮にいれた表面ポテンシャルと表面の電子密度との関係を導出する。これより,電流ドリフトによって電子密度が変化するのに伴う捕獲時定数の変化を計算することが可能となる。最後に,(3)捕獲された電子密度と時間の関係を導出し,ドレイン電流の時間変化を求める。

図8 ドレイン電流ドリフトに関するモデル

また,界面準位が空間的に分布する場合と併せて,(4)単一時定数を有する準位(界面準位が界面に局在している場合に対応する)による捕獲過程に基づくドレイン電流ドリフト特性も比較のため導出する。

## (1) ドレイン電流と捕獲された電子の面密度の関係

$n_{so}$  をゲート電圧が変化した直後の(過剰)電子の面密度とすると、そのときの TFT の線形領域 におけるドレイン電流  $I_{o}$  は次式で与えられる。

$$I_{o} = q \cdot W \cdot \mu \cdot n_{so} \cdot V_{D} / L \tag{1}$$

ただし、ここで q は電子の電荷量、 $\mu$  は電子移動度、 $V_D$  はドレイン電圧、W はチャネル幅、L は チャネル長である。また、時刻 t におけるドレイン電流 I(t) は、次のように表わされる。すなわち、界面に誘起される全電子密度  $N_S$  は印加しているゲート電圧と閾値電圧  $V_T$ 、それに絶縁膜容量  $C_I$  より、

$$N_s = C_1/q \cdot (V_G - V_T) = n_{so} \tag{2}$$

とあらわされる。従って、界面準位に捕獲された電子密度を $n_{st}(t)$ とすると、半導体中の電子の面

密度は  $N_s - n_{st} = n_{so} - n_{st}$  とあらわされるので、そのときのドレイン電流は、

$$I(t) = \mathbf{q} \cdot \mathbf{W} \cdot \boldsymbol{\mu} \cdot (\mathbf{n}_{so} - \mathbf{n}_{st}) \cdot \mathbf{V}_{D} / L \tag{3}$$

となる。

#### (2) 表面ポテンシャルと電子の面密度の関係

(3)式より、時刻とともに界面準位に捕獲された電子の面密度  $n_{st}$  が増加すると、半導体の電子の面密度は減少する。表面における単位体積当たりの電子密度を n とすると、電子の捕獲時定数と電子密度との関係式  $\tau=1/(\sigma \cdot v_{th} \cdot n)$  より、電流ドリフトによってドレイン電流が減少するとともに電子の捕獲時定数が長くなる。

ここで電子密度 n は、 $n=n_o\cdot\exp(q\cdot\psi_s/kT)$ より、表面ポテンシャル  $\varphi_s$ から導かれるのに対して、電子の面密度は、ポアソン方程式から導かれる半導体内の電界強度を用いてあらわされる。ただし、ここで  $n_o$  は、中性領域の単位体積当たりの電子密度であり、フェルミ準位  $E_F$ 、伝導帯の下端  $E_c$ 、伝導帯の有効状態密度  $N_c$  を用いて、 $n_o=N_c\cdot\exp(-(E_c-E_F)/kT)$ とあらわされる。

そこで、表面ポテンシャルと電子の面密度の関係を以下に導く。この時、a-Si: H バルク中に存在する局在準位の密度を知る必要があるが、ここでは、局在準位密度を一定と仮定した。

ゲート電圧によって誘起される半導体中の電荷密度  $\rho$  は、 $\alpha$ -Si: H の場合主として局在準位に捕獲された電子によるものであるので、ゲート電圧により変化する半導体内のポテンシャルを  $\phi$  とすると  $\rho$  は次式であらわされる。

$$\rho\left(\psi\right) = \mathbf{q} \cdot \int_{\mathbf{F}_{n}}^{\mathbf{E}_{F} + \mathbf{q}\psi} \mathbf{g} \cdot d\mathbf{E} \tag{4}$$

これと, ポアソン方程式,

$$\frac{\mathrm{d}^2 \psi}{\mathrm{d} \mathbf{x}^2} = \frac{\rho}{\varepsilon_0 \cdot \varepsilon_S} \tag{5}$$

より、半導体内の電界強度 dy/dx は次式で表わされる。

$$\frac{\mathrm{d}\psi}{\mathrm{dx}} = -\alpha\psi \tag{6}$$

$$\alpha = \sqrt{\frac{q^2 \cdot g}{\varepsilon_0 \cdot \varepsilon_S}}$$

一方, 半導体中の(過剰)電子の面密度 ns は,

$$n_{s} = n_{o} \cdot \int_{0}^{\infty} \left\{ \exp\left(q_{\psi}/kT\right) - 1 \right\} dx \tag{7}$$

とかけるので、(6)、(7)式より、表面ポテンシャルが ♥5の時の電子の面密度は、次式で与えられる。

$$n_{s} = n_{o} \cdot \int_{0}^{\psi_{s}} \frac{\exp(q\psi/kT) - 1}{\alpha\psi} d\psi$$

(8)

#### (3) 捕獲された電子の密度と時間の関係

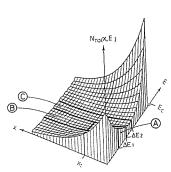

空間的に分布する界面準位の密度分布  $N_{TO}(x, E)$  は,エネルギー E 及び界面からの距離 x の関数である。統一 DIGS モデルによると,界面準位の空間的分布は界面近傍の乱れに起因し,その分布形状は界面の形成プロセスに強く依存する。4.3 節で述べるように,電流ドリフトのふるまいは界面準位の空間的な分布により決定される。x 方向の界面準位の分布は,図一 8 (c) に示すように,x 方向に対して指数関数的に減少する分布と仮定した。これは,この分布が界面近傍に空間分布する界面準位によるみられる分布であること $^{20}$ ,及び次節で示すように実験結果をよく説明する

ことができることによる。

$$N_{TO}(x, E) = N_{ST}(x = 0, E) \cdot exp(-x/x_t)$$

(9)

空間分布をした界面準位への電子の捕獲は、トンネリングを介して行なわれる。この時、電子の波動関数はx方向に対して指数関数的に減少することから、捕獲断面積 $\sigma$ は次式で表わされることが知られている $^{23}$ 。

$$\sigma = \sigma_0 \cdot \exp(-x/x_0) \tag{10}$$

$$x_0 = h/2(2 \cdot m_{eff} \cdot H_{eff}) \tag{11}$$

ただし、ここで  $x_0$  はトンネリング定数、 $m_{eff}$  は電子の有効質量、 $H_{eff}$  は実効トンネリング障壁の高さである。電子の熱速度を  $v_{th}$ 、半導体の電子密度を n とすると、時定数  $\tau$  と捕獲断面積  $\sigma$  の関係式より、

$$\tau = \frac{1}{\sigma \cdot \mathbf{v_{th}} \cdot \mathbf{n}} \tag{12}$$

であるから、(10)、(12)式より、

$$\tau = \tau_0 \cdot \exp(x/x_0) \tag{13}$$

$$\tau_0 = 1/(\sigma_0 \cdot v_{th} \cdot n) \tag{14}$$

となる。

図-8 (c) において、 $x_c$  は電子を捕獲した準位としていない準位の境界を表わしている。 $x_c$  を電子の捕獲した準位の割合が (1-1/e) となる深さであると定義すると、 $x_c$  は時刻 t 及び時定数  $\tau_c$  の関数として次式のようにあらわされる。

$$\mathbf{x}_{c} = \mathbf{x}_{0} \cdot \ln(t/\tau_{0}) \tag{15}$$

このように定義した  $x_c$  を用いると,空間的に分布した界面準位に捕獲された電子の面密度  $n_{st}$  は、斜線で示す部分であらわされ、時刻 t における  $n_{st}$  は次式であらわされる。

$$n_{st} = \int_{-0}^{\infty} \{1 - \exp(-t/\tau_0 \exp(x/x_0)) \cdot N_{TO}(x=0) \cdot \exp(-x/x_t) dx$$

(16)

ここで、 $\tau_0$  が表面の電子密度の関数となっていることに注意されたい。(3)と( $t_0$ )式より、ドレイン電流の時間変化があらわされる。

## (4) 単一の時定数を持つ準位による電流ドリフト

比較のために、界面準位が界面に局在している場合に対応する、単一の捕獲時定数を有する界 面準位によって引き起こされるドレイン電流ドリフトの特性式を導く。

この場合には、捕獲準位密度を  $N_{st}$  とすると捕獲された電子の密度  $n_{st}$  は、次式とであらわされる。

$$\mathbf{n}_{st} = \{1 - \exp(-t/\tau_0)\} \cdot \mathbf{N}_{st} \tag{17}$$

ただし, なは

$$\tau_0 = \frac{1}{\sigma_0 V_{\text{man}}} \tag{18}$$

とあらわされる。この  $n_{st}$  を(3)式に代入することによりドレイン電流の時間的変化があらわされる。 4.3 ドリフト特性の計算と実験結果との対応

本節では,4.2節で導出した式を基に行なった理論計算の結果を示し,実験結果と比較・検討する。理論計算に用いた物理定数を表-2に記す。

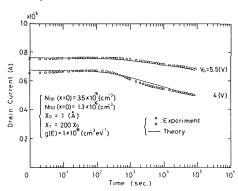

まず,界面準位が界面に局在している場合の,単一の捕獲時定数を有する準位によって引き起こされるドレイン電流ドリフトの計算結果を図-9に示す。理論計算は,種々の捕獲時定数について行なっているが,図-9の点線は捕獲時定数  $\tau_0=53$  [sec.] の計算結果である。  $1\sim10$  秒の範囲以外では計算結果と実験結果は一致しない。また, $\tau_0$  を増加させても理論曲線が時間軸上で平行移動するだけであり,やはり実験結果を再現することができない。このように,単一時定数を有する捕獲過程では,ドレイン電流のドリフトのふるまいを再現することができない。

| 定数名        | 紀 号   | 数 值                     | 雕 位          |

|------------|-------|-------------------------|--------------|

| 電子の電荷量     | q     | 1.602×10 <sup>-19</sup> | с            |

| ボルツマン定数    | k     | 1.381×10 <sup>-23</sup> | 3 - K - 1    |

| 贝克纳电率      | ن ع   | 8.854×10-14             | F·cm-3       |

| 比誘電車       | 6 5   | 11.9                    |              |

| 伝導帯の有効状態密度 | Nc    | 2.8 x 10 1°             | CM.3         |

| 電子の熱速度     | V (h  | 1 × 1 0 ?               | cm·sec1      |

| 電子の移動度     | • μ   | 1 0                     | cm²·V·¹·sec1 |

| 活性化エネルギー   | E E s | 0.45                    | eV           |

| トンネリング定数   | х.,   | 1.0                     | Å            |

| 局在準位密度     | E     | 1 × 1 0 1 e             | cm:\reV-1    |

表 2 理論計算に用いた物理定数

図 10 空間的に分布する界面準位のモデルに 基づく理論計算結果

図9 単一時定数を有する捕獲過程における ドレイン電流ドリフトの理論計算結果

次に、界面準位が空間的に分布するモデルに基づく理論計算結果について述べる。図一5で示した各ゲート電圧におけるドリフト特性に対しての理論計算結果を図一10中に実線で示す。実線の理論計算結果が、各ゲート電圧での全時間領域におけるドリフトのふるまいを非常によく再現していることがわかる。特に、単一時定数の捕獲過程で記述できない長時間にわたる電流ドリフトがよく再現されている。このモデルによると、電子の捕獲過程における時定数分散及び長時間にわたるドリフト現象は、チャネル内の電子の捕獲が、時間とともに界面準位の深さ

方向に進行することで説明される。すなわち、電流ドリフトの時間変化は界面準位の空間的分布で決定される。ここでは、界面準位の空間分布として、 $InP\ MISFET^{22)}$ で見られた(9)式の形を採用している。 $I0^2\sim 10^3$  [sec.] 付近でのドレイン電流の急激な減少は、電子が界面準位に捕獲され始めたことを意味している。また、 $I0^3$  [sec.] 以降でドレイン電流が飽和しているのは、電子の捕獲が界面準位密度の低い値の領域まで進行し、時刻とともに界面準位に捕獲される電子密度が

減少したためであると考えられる。さらに,ゲート電圧の増加とともに捕獲が始まる時間が早くなっているのは,ゲート電圧増加によって半導体表面の電子密度が増し,電子の捕獲時定数が減少したためである。

図 11 界面準位密度のエネルギー 的及び空間的分布形状

図 12 空間的分布する界面準位のモデルに基 づく理論計算結果

以上より、ドレイン電流の長時間にわたるドリフト現象は、界面準位が空間的に分布するモデルで統一的に説明できることが明らかとなった。

#### 5. 結 論

a-Si: HTFTを試作し、ドレイン電流のドリフト現象について実験的及び理論的検討を行なった。その結果、ドレイン電流のドリフト現象は、極めて長い時定数を有し、そのためにドレイン電流のドリフト現象は、複雑なふるまいを示すことが明らかとなった。さらに、十分に初期状態に注意したドレイン電流ドリフトの測定を行ない理論計算と比較検討することにより、ドリフト現象が、空間的に分布した界面準位によるチャネル内電子の捕獲に起因することを明らかにした。

#### 文 献

- 1) A. Madan, P. G. Lecomber and W. E. Spear: J. Non-Cryst. Solids 20 (1976) 239.

- 2) M. Hirose, T. Suzuki and G. H. Dohler: Appl. Phys. Lett. 34 (1979) 234.

- 3) J. D. Cohen, D. V. Lang and J. P. Harbison: Phys. Rev. Lett. 45 (1980) 197.

- 4) H. Okushi, Y. Tokumaru, S. Yamasaki, H. Oheda and K. Tanaka: Jpn. J. Appl. Phys. 20 (1981) L549.

- 5) 渡辺和博:日経マイクロデバイス1月号(1987)41.

- 6) Y. Kuwano, T. Imai, M. Ohnishi, S. Nakano and T. Fukatsu: Jpn. J. Appl. Phys. 19 (1980) Supplement 19 -2, 137.

- 7) 酒巻 久:日経エレクトロニクス 11.16(1987) 207.

- 8) D. L. Steabler and C. R. Wronski: J. Appl. Phys. 51 (1980) 3262.

- 9) D. L. Steabler, R. S. Crandall and R. Williams: Proc. 15th IEEE Photovoltaic Specialists Conf. (1981) 249.

- 10) H. Hasegawa, T. Sawada and H. Ohno: Inst. Phys. Conf. Ser 7 (1984) 569.

- 11) H. Hasegawa and H. Ohno: J. Vac. Sci. Technol. B4 (4) (1986) 1130.

- 12) H. Hasegawa and T. Sawada: J. Vac. Sci. Technol. 16 (1979) 1478.

- 13) H. Hasegawa and T. Sawada: Thin Solid Films 103 (1983) 119.

- 14) M. Shimozuma, K. Kitamori, H. Ohno, H. Hasegawa and H. Tagashira: J. Electron. Mater. 14 (1985) 573.

- 15) M. J. Powell, B. C. Easton and O. F. Hill: Appl. Phys. Lett. 38 (10) 15 (1981) 794.

- 16) M. J. Powell and D. H. Nicholls: IEE PROC. 130 (1933) 2.

- 17) 金子好之, 折村良二, 塚田俊久:電子通信学会技術研究報告 85(1985) ED85-79.

- 18) 平中弘一, 山口忠久, 吉村徹三, 柳沢真太郎:電子通信学会技術研究報告 85(1985) ED85-78.

- 19) 原 毅彦, 有本 智, 沢田孝幸, 大野英男, 長谷川英機:第45回応用物理学会学術講演会講演予稿集(1984)14a-Q-3.

- 20) 原 毅彦, 有本 智, 長谷川英機, 大野英男:電子通信学会技術研究報告 85(1985)ED85-77.

- 21) 有本 智, 金沢 裕, 原 毅彦, 大野英男, 長谷川英機:北海道大学工学部研究報告 127(1985) 1.

- 22) 駱季奎, 沢田孝幸, 大野英男, 長谷川英機, 何 力:電子通信学会技術研究報告 87(1987) ED87-81.

- 23) E. P. Heiman and G. Warfield: IEEE Trans. Electron Devices ED-12 (1965) 167.